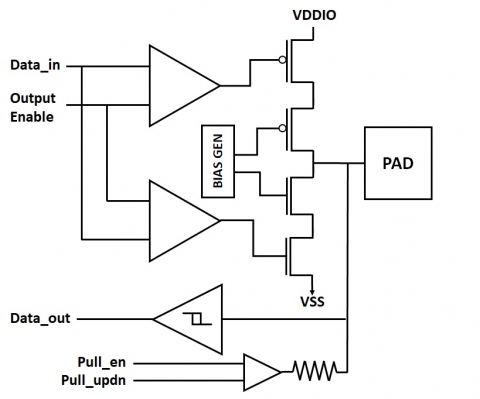

Figure 2 from Low-Loss I/O Pad With ESD Protection for K/Ka-Bands Applications in the Nanoscale CMOS Process | Semantic Scholar

Figure 1 from Flip-chip routing with IO planning considering practical pad assignment constraints | Semantic Scholar

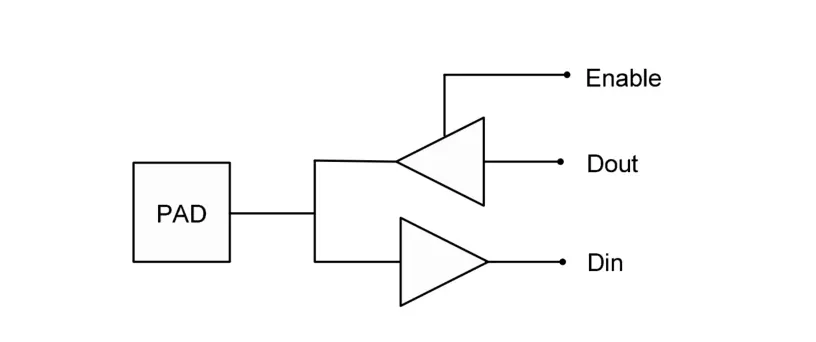

![Mad Life: [ASIC/SoC] PAD 에 대하여 Mad Life: [ASIC/SoC] PAD 에 대하여](http://2.bp.blogspot.com/-YnWTVZWunXM/VFbqHzkDsmI/AAAAAAAAB5s/BHMrVwHOED0/s1600/%EA%B7%B8%EB%A6%BC1.png)